### HACETTEPE UNIVERSITY

DEPARTMENT OF ELECTRICIAL AND ELECTRONICS ENGINEERING

GRADUATION PROJECT

# DESIGN OF A COMPACT IMAGE CAPTURING DEVICE WITH FPGA

PROF. DR. ALİ ZİYA ALKAR

BEDİRHAN ŞAHİN - BURAK DUYSAK - HALİS AYDIN

#### INTRODUCTION

THE INTEREST IN IMAGE CAPTURE AND PROCESSING IS INCREASING DAY BY DAY, AND THE APPLICATION AREAS OF IMAGE CAPTURE AND PROCESSING ARE EXPANDING. LIKEWISE, THE POPULARITY OF "FIELD PROGRAMMABLE GATE ARRAYS (FPGA)" HARDWARE IS INCREASING DAY BY DAY. FPGAS CAN PERFORM MULTIPLE TASKS SIMULTANEOUSLY THANKS TO THEIR PARALLEL PROCESSING CAPABILITIES. FOR THIS REASON, IT IS OFTEN PREFERRED IN APPLICATIONS THAT REQUIRE HIGH SPEED.

IN THIS PROJECT, IT IS AIMED TO DESIGN A COMPACT IMAGE CAPTURE DEVICE USING FPGA AND TO DISPLAY THE REAL-TIME IMAGE CAPTURED BY THE CAMERA IN COMPUTER ENVIRONMENT OVER ETHERNET.

### APPLICATION AREAS

THIS CAPTURE CARD CAN THEN BE DEVELOPED AND USED FOR IMAGE PROCESSING. BECAUSE, THANKS TO ITS PARALLEL PROCESSING SPEED AND THE POWER OF FPGA INNOVATION, THIS PROJECT CAN BE A BUILDING BLOCK FOR IMAGE PROCESSING OR MACHINE LEARNING PROJECTS. IMAGE PROCESSING ALGORITHMS ARE USED IN MANY AREAS SUCH AS SECURITY SYSTEMS, HEALTH SECTOR, RADAR, SATELLITE SYSTEMS. SOME IMAGE PROCESSING ALGORITHMS CAN BE DESIGNED ON FPGA-BASED DEVELOPMENT BOARDS, SUCH AS CHANGING COLOR IN THE IMAGE IN REAL TIME, MORPHOLOGICAL ON AND OFF, RED OBJECT TRACKING, SKIN COLOR RECOGNITION, APPLYING A SOBEL FILTER TO THE IMAGE.

## DIGITAL DESIGN

ALL DIGITAL DESIGNS ARE BASED ON VERILOG AND VHDL CODES.

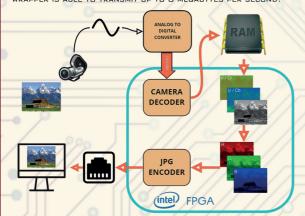

THE ANALOG CAMERA WAS USED WITH THE ADV7180 MODULE, WHICH WAS USED AS AN ANALOG TO DIGITAL CONVERTER. INSIDE THE FPGA FABRIC, CAMERA DECODER, COLOR CONVERSION ALGORITHMS, JPEG ENCODER ALGORITHM, UDP WRAPPER, AND ETHERNET CONTROLLER IS APPLIED. THE 64 MB CMOS SDRAM IS USED FOR FRAME BUFFERING. JPEG ENCODER IP CORE

The input image to JPEG Encoder is 640x480 24-bit RGB color. 7.3 ms processing time @ 100 MHz clock [2.3 clock cycles per input sample]

INPUT FILE SIZE = 921 KB. DUTPUT FILE SIZE = 44 KB (DEPENDS ON

#### ETHERNET IP CORE

THE ETHERNET IP CORE IS A 10/100 MEDIA ACCESS CONTROLLER (MAC). IT CONSISTS OF A SYNTHESIZABLE VERILOG RTL CORE THAT PROVIDES ALL FEATURES NECESSARY TO IMPLEMENT THE LAYER 2 PROTOCOL OF THE ETHERNET STANDARD. AT FULL BLAST, THE UDP WRAPPER IS ABLE TO TRANSMIT UP TO B MEGABYTES PER SECOND.

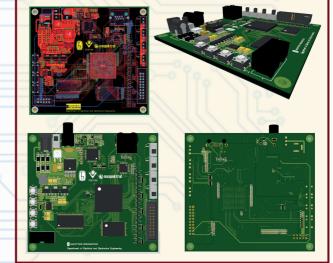

### HARDWARE DESIGN

BASED ON THE DESIGN REQUIREMENTS, OUR PROJECT'S SCHEMATIC DESIGNS AND PCB LAYOUT ARE DESIGNED USING ALTIUM DESIGNER SOFTWARE.THE IMAGES SHOW THE PCB LAYOUT OF THE SYSTEM DESIGNED FOR HARDWARE IMPLEMENTATION.

THE DESIGNED STRIFF CONSISTS OF MANY BUILDING BLUCKS. THESE ARE 64MB-SDRAM, 32MB-FLASH MEMORY, ETHERNET CONTROLLER AND MULTIFORMAT SDTV VIDEO DECODER. OUR DESIGN FEATURES EP2C35F4B4CB FPGA CYCLONE® II FAMILY PROCESSOR. THE DESIGNED PCB LAYOUT IS AN 8-LAYER BOARD DESIGN WITH DIMENSIONS OF 100MMX110MM.

### ACKNOWLEDGEMENTS

THIS PROJECT WAS COMPLETED WITHIN THE CONTEXT OF ELE401-402 GRADUATION PROJECT COURSES IN HACETTEPE UNIVERSITY, FACULTY OF ENGINEERING, DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING.

WE THANK PROF.DR. ALI ZIYA ALKAR FOR HIS INVALUABLE CONTRIBUTIONS TO OUR PROJECT.

WE WOULD LIKE TO THANK TÜBİTAK FOR PROVIDING A GREAT OPPORTUNITY WITH THE "2209-A UNIVERSITY STUDENTS RESEARCH PROJECTS SUPPORT PROGRAM" AND MS SPECTRAL FOR THEIR FINANCIAL SUPPORT.